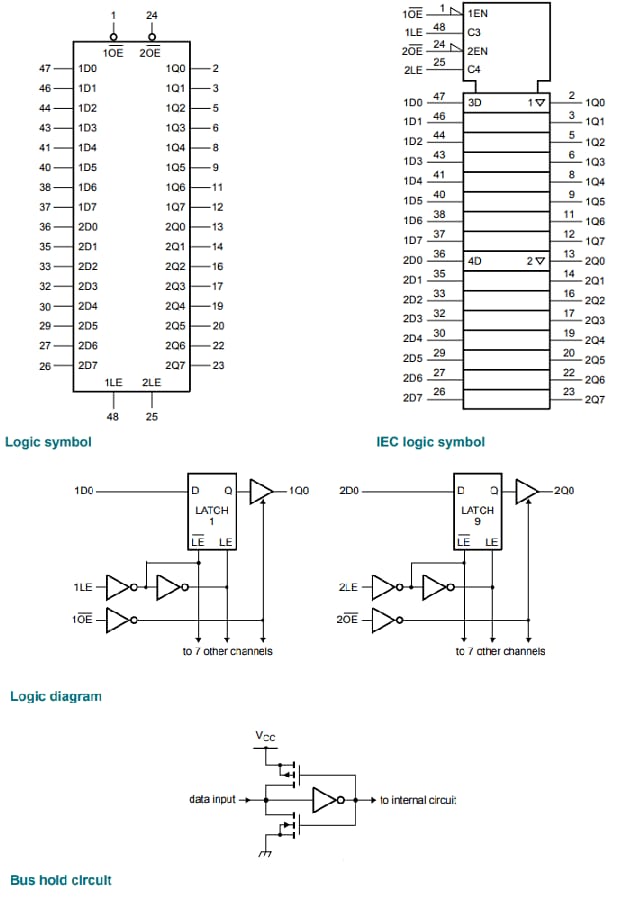

74LVC(H)16373A 16位D型透明锁存器采用CMOS技术,具有低功耗和多字节流通标准引脚分配架构。这些器件由两个部分组成,包括八个D型透明锁存器,具有三态真输出。当LE为高电平时,Dn输入端的数据进入锁存器。在该情况下锁存器透明,即每当相应的D输入改变时锁存器输出就会改变。

特性

- 连接5V逻辑时,存在5V容限输入/输出

- 1.2V至3.6V宽电源电压范围

- CMOS低功耗

- 多字节流通标准引脚分配架构

- 多个低电感电源引脚,可最大限度降低噪声和接地弹跳

- 直接与TTL电平接合

- 所有数据输入均具有总线保持功能(仅限74LVCH16373A-Q100)

- 指定温度范围:-40°C至85°C及-40°C至125°C

- VCC=0V时具有高阻抗

- 符合JEDEC标准:

- JESD8-7A(1.65V至1.95V)

- JESD8-5A(2.3V至2.7V)

- JESD8-C/JESD36(2.7V至3.6V)

- ESD保护:

- MIL-STD-883, 方法3015超过2000V

- HBM JESD22-A114F超过2000V

- MM JESD22-A115-A超过200V(C=200pF,R=0Ω)

- CDM ANSI/ESDA/Jedec JS-002超过1000V

功能图

View Results ( 4 ) Page

| 物料编号 | 数据表 | 电路数量 | 逻辑类型 | 逻辑系列 | 输出线路数量 | 高电平输出电流 | 传播延迟时间 | 电源电压-最小 | 电源电压-最大 | 通道数量 | 输入线路数量 | 封装 / 箱体 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 74LVC16373ADGG,118 |  |

2 Circuit | CMOS | LVC | 16 Line | - 24 mA | 12 ns at 1.2 V, 3 ns at 3.3 V | 1.2 V | 3.6 V | 16 Channel | 16 Line | TSSOP-48 |

| 74LVCH16373ADGG:11 |  |

2 Circuit | CMOS, TTL | LVCH | 16 Line | - 24 mA | 6 ns | 1.2 V | 3.6 V | 2 Channel | 16 Input | TSSOP-48 |

| 74LVC16373ADGVJ |  |

2 Circuit | CMOS, TTL | LVC | 16 Line | - 24 mA | 6 ns | 1.2 V | 3.6 V | 2 Channel | 16 Input | TVSOP-48 |

| 74LVCH16373ADGVJ |  |

2 Circuit | CMOS, TTL | LVCH | 16 Line | - 24 mA | 6 ns | 1.2 V | 3.6 V | 2 Channel | 16 Input | TVSOP-48 |

发布日期: 2019-05-27

| 更新日期: 2023-04-26