特性

- Z85C30:优化用于非多路复用总线微处理器

- Z80C30:优化用于多路复用总线微处理器

- 跟NMOS型号引脚兼容

- 两个独立的0至4.1Mbps全双工通道,每个通道均设有独立的晶体振荡器、波特率发生器 (BRG) 和用于时钟恢复的数字锁相环 (DPLL)

- 程序控制下的多协议运行;可编程用于NRZ、NRZI或FM数据编码

- 异步模式,每个字符具有5至8位和1、1½或2个停止位、可编程时钟因子、中断检测和生成;奇偶校验、超限和组帧错误检测

- 同步模式,在1或2个同步字符上实现内部或外部字符同步,并通过CRC-16或CRC-CCITT预设为1s或0s进行CRC生成和检查

- SDLC/HDLC模式,具有全面的帧级控制、自动零插入和删除、I-Field残留处理、中止生成和检测、CRC生成和检查,以及SDLC环路

- 软件中断确认功能(NMOS不可用)

- 本地环回和自动回声模式

- 支持T1数字Trunk76

- 增强型DMA支持(NMOS不可用)、10x19位状态FIFO和14位字节计数器

- 速度:

- Z85C3O:8.5MHz、10MHz和16.384MHz

- Z80C3O:8MHz和10MHz

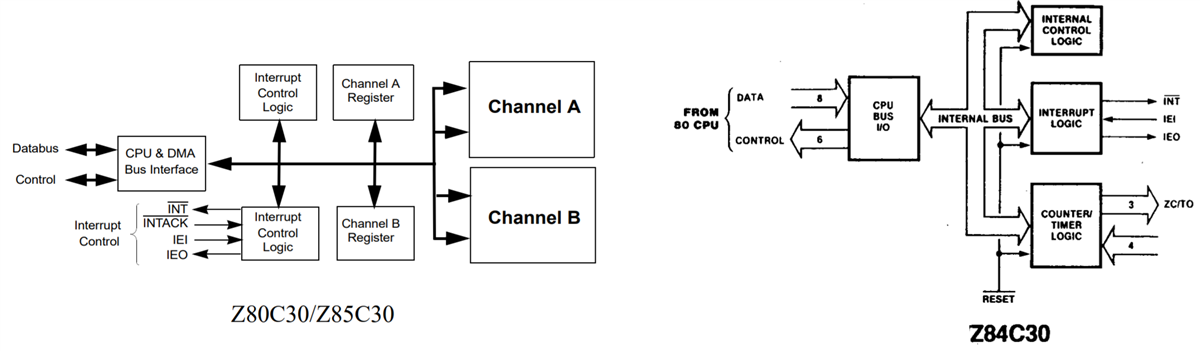

功能框图

发布日期: 2021-11-15

| 更新日期: 2025-05-12